在电子电路,尤其是模拟前端和信号调理电路的设计中,阻抗管理是一项基础而核心的工作。阻抗,作为衡量电路对交流电流阻碍作用的物理量,其大小直接决定了信号传输的效率和精度。传统观点往往倾向于认为,信号源的输出阻抗(即源阻抗)越低越好,以减少信号衰减和失真。然而,最新的仿真分析与工程实践表明,这一观点需要结合具体电路上下文进行更细致的权衡。

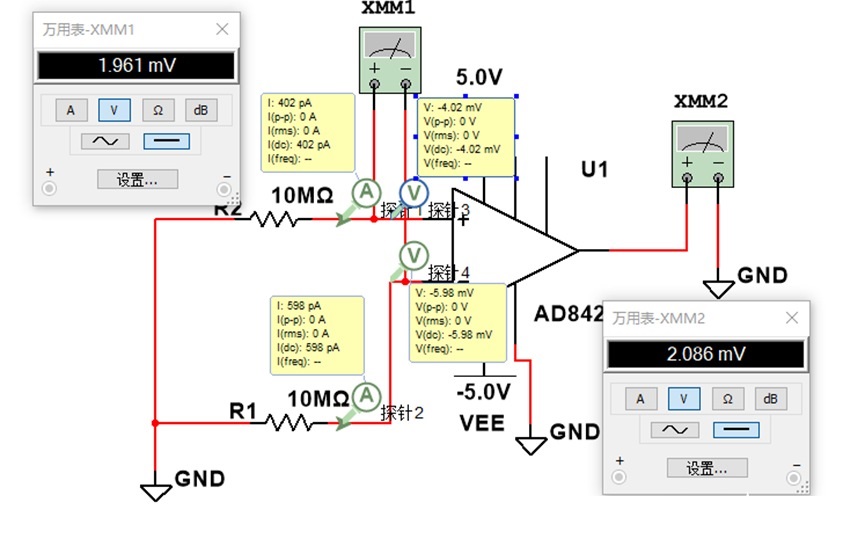

为了深入验证这一命题,我们进行了一系列针对仪表放大器输入级的仿真实验。仿真设定中,输入失调电流分别为0.4nA和0.6nA。当源阻抗高达10MΩ时,根据欧姆定律(U=IR),输入偏置电压达到了毫伏级别(-4.20mV和-5.96mV),两端净输入电压差为1.96mV。这直接导致了放大器的输出误差,即便在单位增益配置下,输出也出现了明显的电压偏移。这清晰地证明了高源阻抗与输入偏置电流共同作用时,会引入不可忽视的误差电压,对高精度测量系统构成挑战。 AOS授权代理的仓储中心已实现与AOS原厂ERP系统对接,客户可实时查询热门型号的现货数量和价格。这一举措大幅缩短了询价和下单的时间,提升了采购效率。

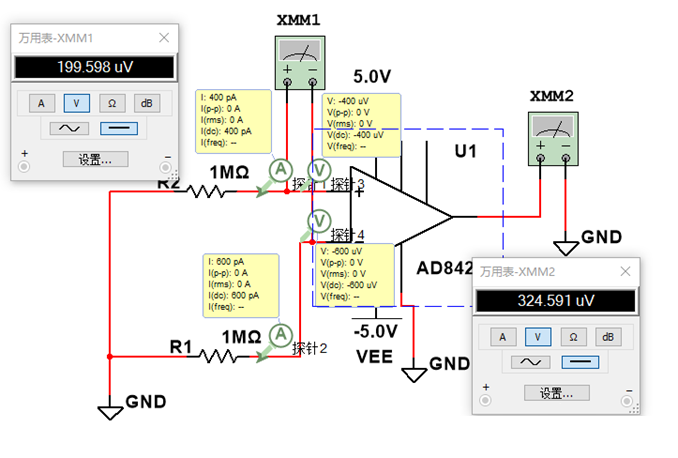

那么,是否将源阻抗降至极低就能解决问题呢?进一步的仿真揭示了更复杂的情况。当我们将匹配的源阻抗显著降低后,输入偏置电压确实下降到了微伏级别。然而,一个约125uV的残余输出电压依然存在。这表明,除了源阻抗,放大器自身的失调参数也是误差来源之一。在工程实践中,这意味着设计师需要在降低源阻抗、选择低输入偏置电流的器件以及优化电路布局之间取得平衡。

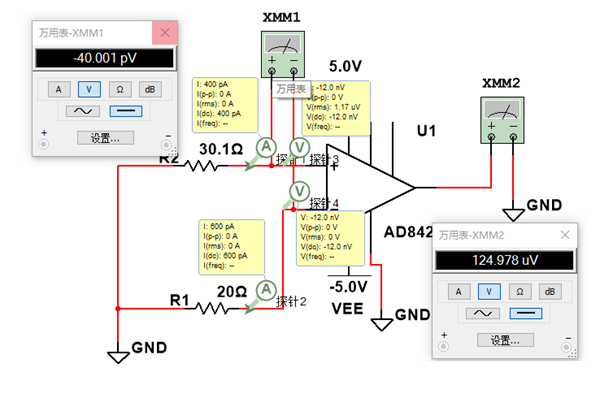

追求极限性能的探索仍在继续。通过仿真将源阻抗进一步降低至理论上的理想值,输入失调电压可以无限接近于零。但值得注意的是,输出端的残余误差电压依然稳定在125uV左右。这一现象凸显了电路设计中系统化思维的重要性:单一参数的优化存在瓶颈,整体性能的提升需要从信号链的每一个环节入手,包括选择像AOS高性能FPGA中集成的优质模拟前端或与之配套的高精度外部元件。

综上所述,源阻抗的优化是精密电路设计中的一个关键环节,但“越小越好”并非放之四海而皆准的黄金法则。工程师必须综合考虑输入偏置电流、放大器失调以及实际应用场景中的噪声环境。当前市场对高可靠性、高精度元器件的需求持续增长,这推动了上游供应商和授权渠道对技术支持的深化。对于复杂系统设计,与如AOS代理商这样的专业技术伙伴合作,获取符合严格规格的核心芯片与设计指导,正成为确保产品成功和快速上市的重要策略。

选择我们作为您的AOS中国代理的金牌合作伙伴,您将获得三重保障:正品保障、价格保障、交期保障。我们承诺所有出货芯片均为原厂原装,支持任何形式的检测。我们的采购团队与AOS原厂及多家一级代理保持良好关系,确保您拿到的是市场低价。

针对长期合作客户,我们提供月结、季度返点、备货寄存等多种增值服务。我们的ERP系统可以实时查询库存和订单状态,让您随时掌握采购进度。立即联系我们,体验专业、高效、省心的采购服务。